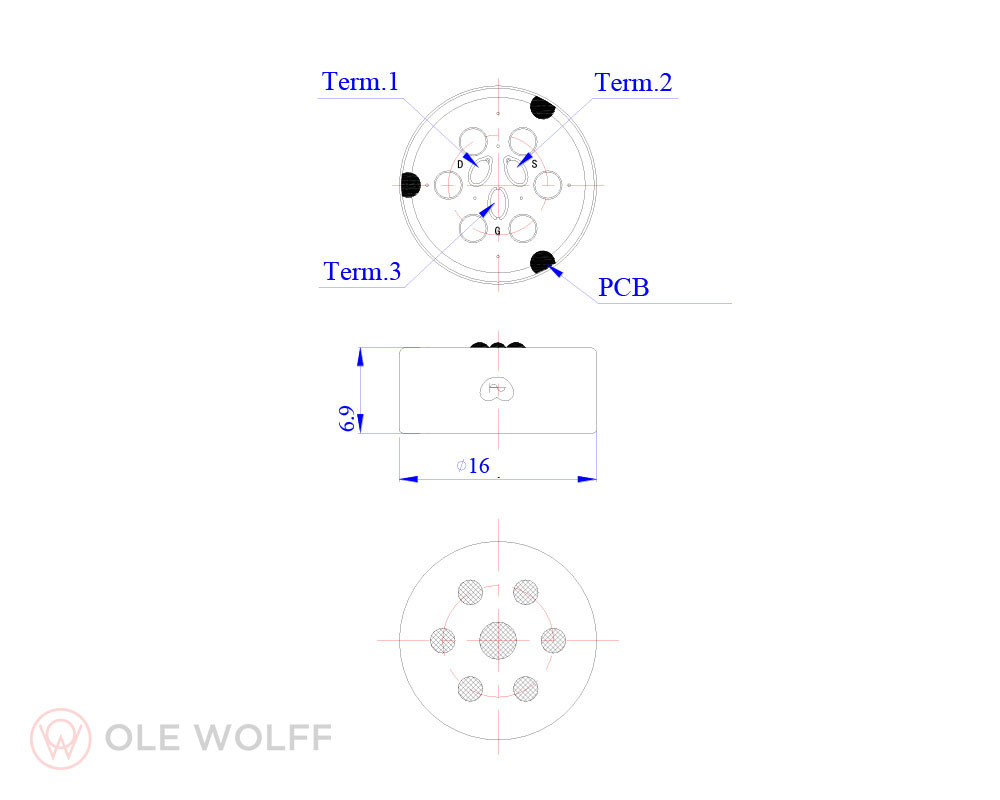

OWMU-1669T-44

ECM microphone

Characteristics

Specifications are subject to change without prior notice. Upon request Ole Wolff can supply further specifications, simulation parameters etc.

Additional characteristics

Sleep mode

Test conditions (unless otherwise specified in the table): VDD= 1.8V, fclock= 350kHz, values: TA= 25°C. Max/min values: TA= -20°C to 70°C.

Specification | Symbol | Test Conditions | Min. | Typ. | Max. | Unit |

Clock Frequency | Fc | 350 | kHz | |||

Current Consumption | I | Fclk=0kHz | 1 | uA | ||

Current Consumption | I | Fclk=350kHz | 50 | uA |

General microphone specification(Test condition: Vdd=1.8V, Fclk=2.4MHz)

Specification | Symbol | Test Conditions | Min. | Typ. | Max. | Unit |

Supply Voltage | Vdd | 1.62 | 1.8 | 3.6 | V | |

Low Frequency rolloff | LFRO | -3dB relative to 1kHz | 32 | Hz | ||

High Frequency Flatness | +3dB relative to 1kHz | 15 | kHz | |||

DC Output | Full scale=±100 | - | 0 | - | %FS | |

Polarity | Increasing sound Pressure | Increasing density of 1’s | ||||

Data Format | ½ Cycle PDM | |||||

Short Output Current | Isc | DATA PIN Short to GND | 1 | 20 | mA | |

Output Load | Cload | 150 | pF | |||

Fall Asleep Time | Tslp | Fclk< 350kHz | 20 | us | ||

Wake-up Time | Twk | Fclk> 350 kHz | 20 | ms | ||

Power Up Time | Tpu | Time to start up in any mode after VDD off for >10ms, CLOCK remained on. | 20 | ms | ||

Start time | Time to start up in any mode after VDD and CLOCK applied. | 50 | ms | |||

Mode Change Time | Tmc | Time to switch between modes. VDD remains on. | 20 | us | ||